BCH Decoder

Features

- BCH decoder compliant with the DVB-T2/S2 standard.

- Available for Altera/Xilinx FPGA or ASIC implementation.

- High speed design.

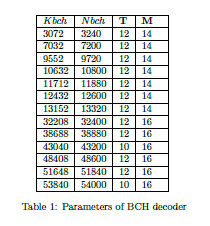

- BCH decoder works on GF(2M) where M = 16 or 14 and correctup to T errors where T = 10 or 12.

- Area and power optimized implementation.

- Compatible flexible and easy integrated with other modules.

Functional Description

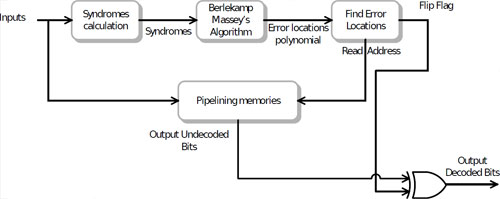

The BCH decoder has four main functional blocks along with memory blocks. Syndrome calculation block calculates syndrome components which tell about presence of errors in the encoded data. Brelekamp Massey's algorithm block computes error locator polynomial whose inverse of roots gives error locations. A polynomial solver in find error location unit solves this error locations polynomial and gives error locations indicated. For binary decoding the correction value will be just the flip of the error value which can be done using XOR gate only.

Parameters

Performance

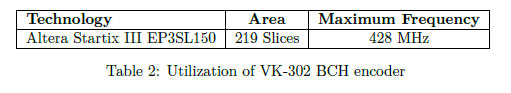

- Synthesis results for the BCH Encoder are shown in Table 2, with total latency between input and output equal parity length clock cycles

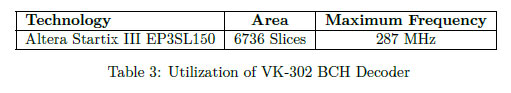

- Synthesis results for the BCH Decoder are shown in Table 3, with total latency between input and output equal code length + 786 clock cycles.

IP Deliverables

- Synthesizable Verilog

- System Model (Matlab) and documentation

- Verilog Test Benches

- Documentation

Download