DVB C Demodulator

System Overview

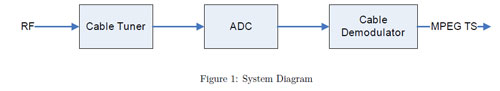

The demodulator is designed to be used together with a cable tuner and an analog to digital converter (ADC).

The system has an internal state machine to control the operation, which can be externally configured via the SPI interface. A typical system application is shown in Figure 1.

This DVB-C QAM demodulator is supplied as a portable and synthesizable Verilog-2001 IP. The system is designed to be used in conjunction with a standard cable tuner. The QAM signal is acquired blindly, and QAM signal constellations from QAM 16 through QAM 256 are supported. The operation of the demodulator is automated by a master finite state machine.

Features

- DVB-C EN 300 429 & ITU-T J.83 Annex A & Annex C compliant QAM demodulator

- Supports IF input

- QAM constellations 16, 32, 64, 128 and 256

- Symbol rates up to 7 MBaud

- Blind acquisition of QAM constellation sizes

- Parallel and Serial MPEG outputs

- 3 external clocks, or 2 external, 1 internally generated

- SPI port (Slave) to external processor

Functional Description

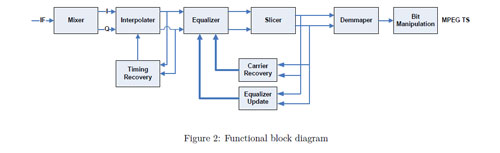

The design interfaces to an external analog to digital converter, which receives the analog signal from the external tuner. The incoming IF signal is sampled at a rate greater than four times the maximum symbol rate.

Hence, for symbol rates up to 7 MBaud, the sampling rate is around 28 MHz.

As shown in Figure 2, the digital signal is first mixed down to baseband. The included blind frequency correction can compensate for ±170 kHz frequency offsets. The timing correction can correct up to 100 ppm. acquisition.

The equalizer in the chip can be configured as fractional or symbol spaced. It acquires the QAM signal without a training sequence, in blind mode, and then tracks the signal in the decision-feedback mode.

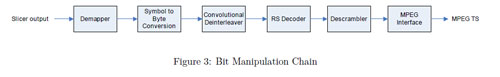

Signal degradation due to impulse noise in cable systems is overcome using a combination of convolutional interleaving and Reed-Solomon error correction, as illustrated in Figure 3. The most significant bits of the demodulated I/Q symbols are differentially decoded to obtain a rotation invariant constellation. The QAM symbols are then demapped into a bit stream, according to the definitions provided by DVB. Each symbol yields four bits for QAM 16, five for QAM 32, six for QAM 64, seven for QAM 128 and eight for QAM 256.

The bit-stream is aligned into bytes, which are in turn aligned into 204 byte frames. These are then fed to a (204,188) Reed-Solomon (RS) decoder, which is capable of correcting eight byte errors per frame. The design also keeps track of the corrected errors, giving an indication of the received signal quality. Frames with more than eight errors are regarded as uncorrectable, and are flagged. This gives an indication of the quality of the MPEG output.

The decoded packets are then applied to a descrambler to reverse the energy dispersal introduced by the transmitter. Finally, the output is presented as a stream of regularly spaced MPEG packets.

Applications

- Set-top boxes

- Cable receivers

- Digital cable ready TV sets

IP Deliverables

- Synthesizable Verilog

- System Model (Matlab) and documentation

- Verilog Test Benches

- Documentation

- FPGA testing environment

The DVB-C demodulator is coded in Verilog-2001. No third-party Intellectual properties are contained in this product. Performance evaluation was completed using an XtremeDSP Spartan-3A DSP development board on a Xilinx Spartan-3A DSP 3400 device.

Download