DVB-T2 Demodulator

System Overview

The demodulator is designed to be used together with a cable tuner and an analog to digital converter (ADC).

The system has an internal state machine to control the operation, which can be externally configured via the SPI interface. A typical system application is shown in the following figure.

This DVB-T2 QAM demodulator is supplied as a portable and synthesizable Verilog-2001 IP. The system was designed to be used in conjunction with a standard RF tuner. QAM signal constellations are supported, including QAM16, QAM64 and QAM256. QPSK, and BPSK also supported. The operation of the demodulator is automated by a master finite state machine.

Features

- DVB-T2 EN302 755 V1.2.1, Rev.9 compliant OFDM demodulator

- Supports IF input

- QAM constellations 16, 64 and 256

- QPSK, and BPSK also supported

- Parallel and Serial MPEG outputs

- 3 external clocks, or 2 external, 1 internally generated

- SPI port (Slave) to external processor

Functional Description

The design interfaces to an external analog to digital converter, which receives the analog signal from the external tuner.

The included frequency correction can compensate for 500KHz frequency offsets for 8MHz channel bandwidth.

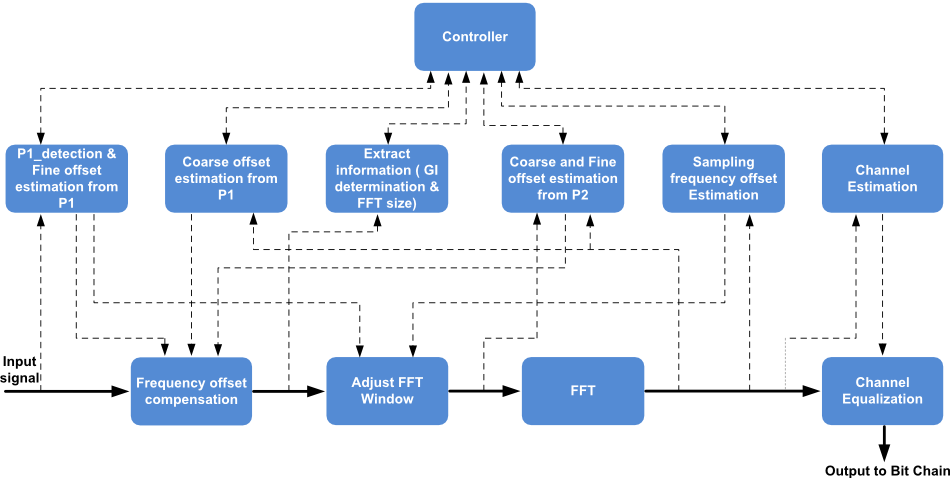

As shown in the following figure, the digital signal is first mixed down to baseband.

The chip automatically locks on to the supported BPSK, QPSK and QAM constellation in the set 16, 64, and 256, using data aided acquisition.

The synchronization block is capable of all forms of synchronization, including frame, symbol, frequency synchronization, as well as clock recovery, either from scattered pilots, or using all pilots (tracking mode). The P1 symbol is used for frame synchronization, and the P2 symbols are used for acquisition mode.

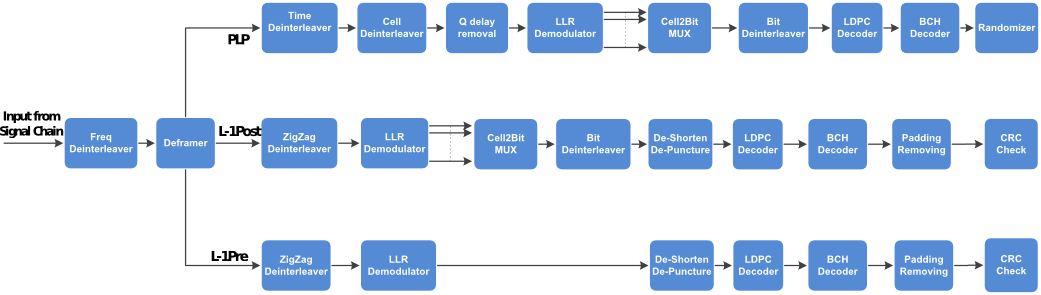

Signal degradation due to impulse noise in cable systems is overcome using a combination of interleaving,

BCH error correction, and Low Density Parity Check (LDPC) as illustrated in the following figure.

The bit interleaved coding and modulation (BICM) chains are provided for data, L1-pre and L1-post signalling. The data bit chain demodulates the incoming data stream using either 2D log-likelihood ratio (LLR) demapping, or 1D LLR, depending on whether the constellation rotation is done in the transmitter, or not. The low density parity check (LDPC) block and the BCH decoder deal with short frame and normal frame types. The LDPC decoder decodes iteratively following the layered belief propagation algorithm. The BCH decoder can correct upto 12 bits, or 10 bits per frame, depending on the frame type and coding rate.

The other two BICM chains are used for signalling and parameter passing.

The decoded packets are then applied to a descrambler to reverse the energy dispersal introduced by the transmitter. Finally, the output is presented as a stream of regularly spaced MPEG packets.

Applications

- Set-top boxes

- Digital TV receivers

IP Deliverables

- Synthesizable Verilog

- System Model (Matlab) and documentation

- Verilog Test Benches

- Documentation

- FPGA testing environment

The DVB-T2 demodulator is coded in Verilog-2001. No third-party Intellectual properties are contained in this product. Performance evaluation was completed using an using an Altera DE3 development board on an Altera Stratix III LS150 device.

Download