FFT Stage

System Overview

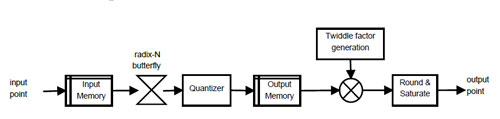

The FFT/IFFT engine is a parametrized FFT stage used as the main building block for FFT/IFFT/DFT blocks.

Features

- Supports radix-2, 3, 4 and 5

- Parametrized (radix, internal quantization, and FFT size)

- Used as a building block for FFTs and DFTs

- Configurable versatile design

Functional Description

- Using a single radix-N butterfly, and twiddle factor multiplication.

- Quantization at butterfly output: BSATLEN determines number of bits to saturate, OPWIDTH deletermines number of bits to round/truncate, QUANTIZE determines quantization method ('ROUND' for rounding).

- Round/Saturate after twiddle factor multiplication: TWIDTH-1 bits (currently TWIDTH has a fixed value of 12) are rounded, TWDLSAT determines wether to saturate (1 single bit) or not.

Applications

- 3GPP LTE

- IEEE 802.16 WiMax

- DVB

- xDSL

IP Deliverables

- Synthesizable SystemVerilog

- System Model (Matlab code) and documentation

- SystemVerilog Test Benches

- Documentation

Latency

The latency between input point number RADIX−1 RADIX ×FFTSIZE and the first output point is: Butterfly latency + Twiddle generation latency + 3 cycles.

Butterfly latency is 1 cycle for radix-2 butterfly, 2 cycles for radix-4 butterfly, 3 cycles for radix-3 butterfly, and 5 cycles for radix-5 butterfly. Twiddle multiplication latency is 2 cycles for radix-4, and 0 for other radixes or when 'FFTSIZE' is the same as 'RADIX'.

Download