LDPC Decoder IS-GPS-800D

Features

- Irregular parity check matrix

- Layered Decoding

- Minimum sum algorithm

- Configurable number of iterations

- Soft decision decoding

- IS-GPS-800D compliant

Functional Description

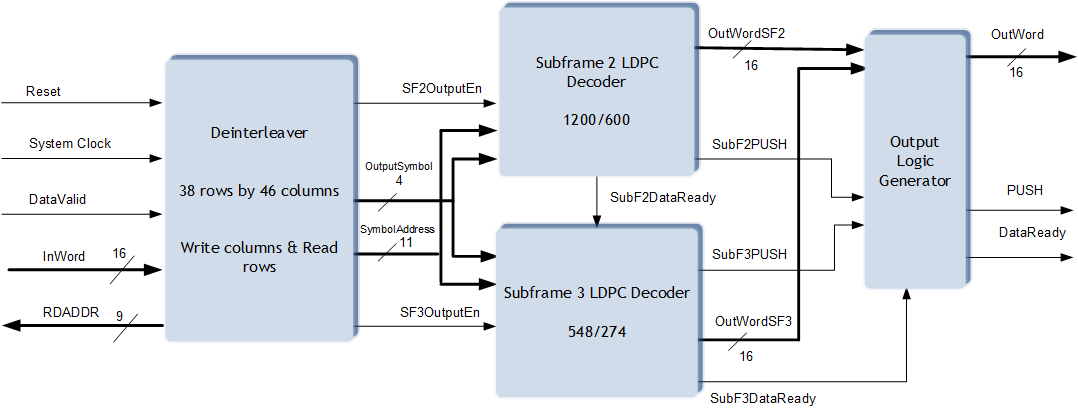

The IS-GPS-800D standard defines an irregular Parity Check Matrix (PCM) for 2 subframes (2 and 3) encoded using Low Density Parity Check (LDPC) Forward Error Correction (FEC). Subframe 2 has a total of 600 bits and subframe 3 has a total of 274 bits. Both subframes are separately encoded using rate 1/2 LDPC codes. In effect, there are 1200 symbols (coded bits) for subframe 2, and 548 symbols (coded bits) for subframe 3.

The VK3061 LDPC IP implements the error correction module in the GPS receiver, as well as the memories. It integrates the de-interleaver, subframe 2 LDPC decoder and subframe 3 LDPC decoder with both the DPRAM and the FIFO. The block diagram for the LDPC IP is shown in the Figure. 1.

IP Deliverables

- Synthesizable Verilog

- System Model (Matlab) and documentation

- Verilog Test Benches

- Documentation

Download