ZigBee Tranceiver PHY

Features

- Low power transceiver PHY IP for ZigBee applications, compliant with IEEE 802.15.4 standard.

- Efficient demodulator with frame synchronization and frequency offset compensation.

- Supports 2 MHz IF input (reconfigurable on request).

- Offset-QPSK (OQPSK)

- Chip rate: 2000 kchips/sec

- Bit rate: 250 kbits/sec

- Symbol rate: 62.5 ksymbols/sec

- Spreading sequence: 16-ary orthogonal

- Support a carrier frequency offset (CFO) up to 250 KHz

- Sampling frequency: 8 MHz (reconfigurable on request)

- Uses single-bit limiter (8-bit ADC version available on request)

- AHB-Lite bus interface (other interfaces available on request)

Functional Description

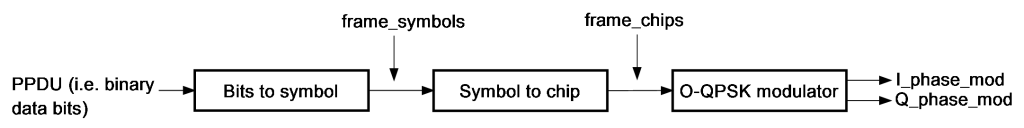

The modulation and spreading functions for the O-QPSK PHYs are processed through 3 steps. First, each 4 bits are gathered to represent 1 symbol which has a value from 0 to 15. Second, each symbol is used to select among 16 PN sequences called chip. Finally, each chip is modulated using O-QPSK with half-sine pulse shaping.

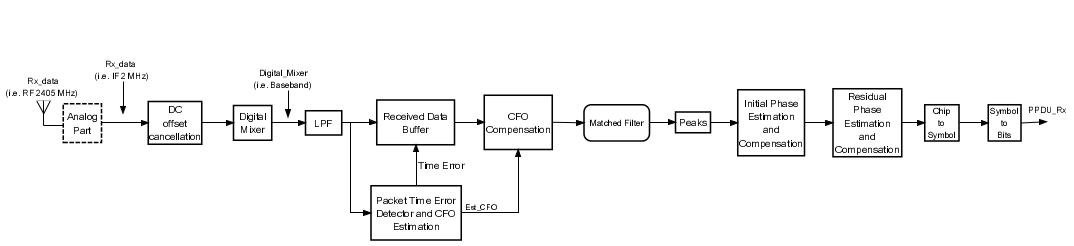

Once a preamble is detected, the Start of Frame Delimiter (SFD), frame length, and other receiver status information is sent to the upper layer. Additionally, the payload data is written to the received data buffer to create the PSDU packet, which is transferred to the MAC layer when requested. The PHY notifies the MAC layer for arrival of MAC Protocol Data Unit (MPDU) along with the LQI information via an interrupt. If a valid preamble is not detected, it gives feedback to the packet time error detection block to restart the energy detection process. The design includes ED and LQI circuits to support CCA modes by MAC defined in IEEE 802.15.4.

The design includes a standard 32-bit AHB-lite, slave interface version 3.0, with registers as defined in the Register Description section of the Datasheet.

Applications

- Home automation

- Health care

- Smart energy

- Smart metering Utility Network (SUN)

IP Deliverables

- Synthesizable Verilog

- System Model (Matlab) and documentation

- Verilog Test Benches

- Documentation

Download